# External interfaces in series Vortex86MX SoC

# GPIO, PWM/SERVO, SPI, I2C, COM

Document version 1.1 7/2012

#### Content

| 1. Valid models                              | 3  |

|----------------------------------------------|----|

| 2. Connector description                     | 3  |

| 3. Function block diagram                    | 5  |

| 4. VCC                                       | 7  |

| 5. GPIO – General Purpose Input Output ports | 7  |

| 5.1. Pinout                                  | 7  |

| 5.2. Electrical characteristics              |    |

| 5.3. Programming                             |    |

| 5.4. GPIO vs. BIOS Setup                     | 9  |

| 5.5. Performance                             | 9  |

| 6. SPI – Serial Peripheral Interface bus     |    |

| 6.1. Characteristics                         |    |

| 6.2. Pinout                                  |    |

| 6.3. Programming                             | 11 |

| 7. I2C – Inter integrated Circuit interface  |    |

| 7.1. Characteristics                         | 12 |

| 7.2. Pinout                                  | 12 |

| 7.3. Programming                             | 13 |

| 8. Serial ports                              | 14 |

| 8.1. Characteristics                         | 14 |

| 8.2. Pinout                                  | 15 |

| 8.3. Programming                             | 15 |

| 9. PWM - Pulse Width Modulation              |    |

| 9.1. Pinout                                  | 16 |

| 9.2. Electrical characteristics              | 16 |

| 9.3. Performance                             | 16 |

| 9.4. Programming                             | 17 |

| 10. Microcontroller 8051 notice              | 17 |

| 11. Software libraries                       | 18 |

| 11.1. RoBoIO library                         |    |

| 11.2. How to use                             |    |

| 12. Appendix A - Technical Reference         |    |

#### 1. Valid models

Information provided in this manual fully valid for series with externalized GPIO/PWM/SPI/I2C ports

| TC-261MXI   | GPIO, 3x RS232, 512MB RAM           |

|-------------|-------------------------------------|

| TC-261MXGI  | GPIO, 3x RS232, 1GB RAM             |

| TC-261MXIC  | GPIO, 1x RS485, 2x RS232, 512MB RAM |

| TC-261MXGIC | GPIO, 1xRS485, 2x RS232, 1GB RAM    |

There are models with same structure which does not have GPIO header external. For them are information also valid but does not have practical usage, because missing physical interface there. Here just for notice:

a) only information related with COM ports valid for:

| TC-261MXC  | 2x RS232, 1x RS485, 512MB RAM |

|------------|-------------------------------|

| TC-261MXGC | 2x RS232, 1x RS485, 1GB RAM   |

b) none externalized interface are on models:

TC-261MXH TC-261MXGH TC-261MXK

#### 2. Connector description

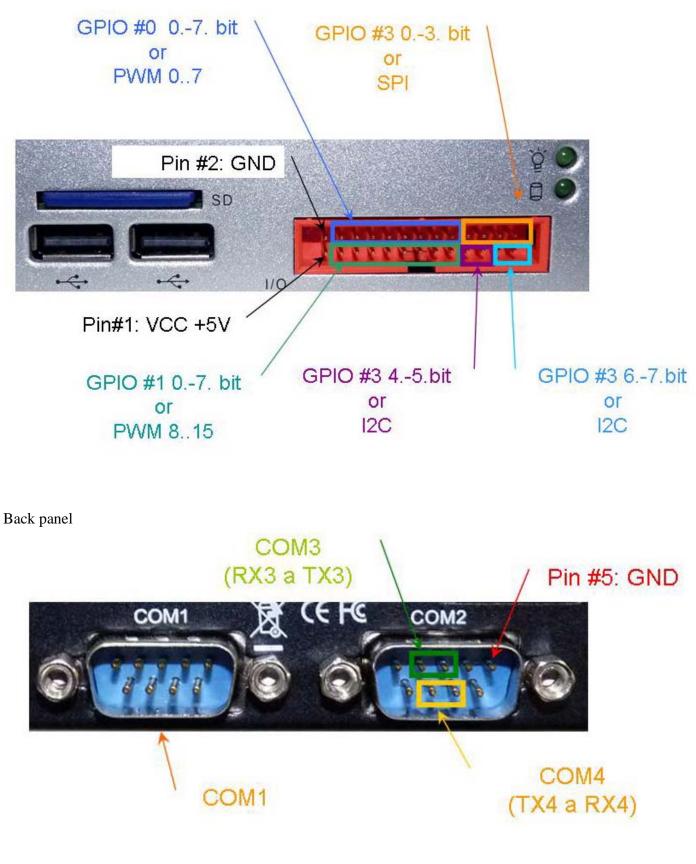

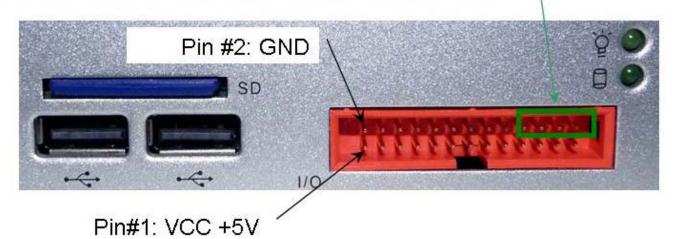

Devices have on front panel multipurpose box header 26-pin. This is connector 2 row, 2x13, pitch 2.54mm. Many suppliers provide this connector typically for flat cables

As you can see from picture there is available power pin, GND and sets of GPIO, PWM, SPI and I2C pins. Their functionalities are possible to select in BIOS Setup or by programming PCI register in run time. So their can be also switched during operations by user's application.

Totally there are available ports:

GPIO: 3 groups of ports, each with 8-bit input/output, totally 24 bit

PWM: 2 groups, each with 8-bit, totally 16 PWM ports

- SPI: 1 port

- I2C: 2 ports

- COM: 3 ports

External interfaces Vortex86MX series

Front panel

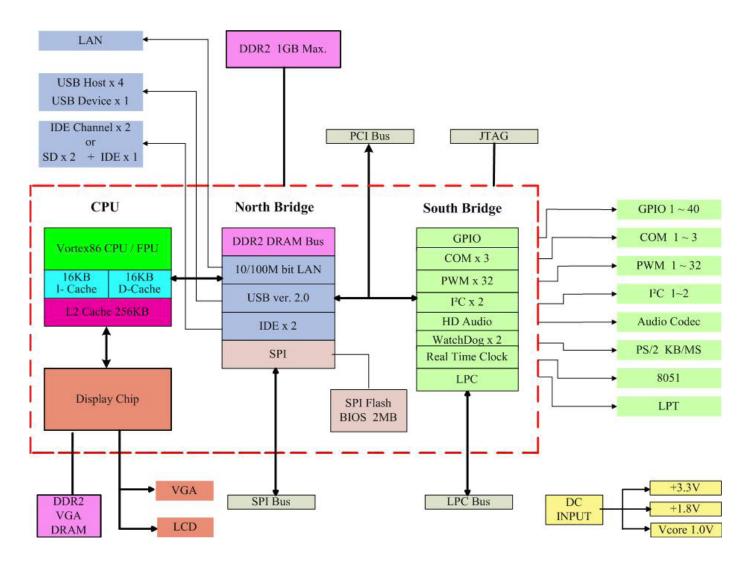

## 3. Function block diagram

Vortex86MX provides several types of interfaces for general usage in the system.

Refer to Vortex86MX functions block diagram:

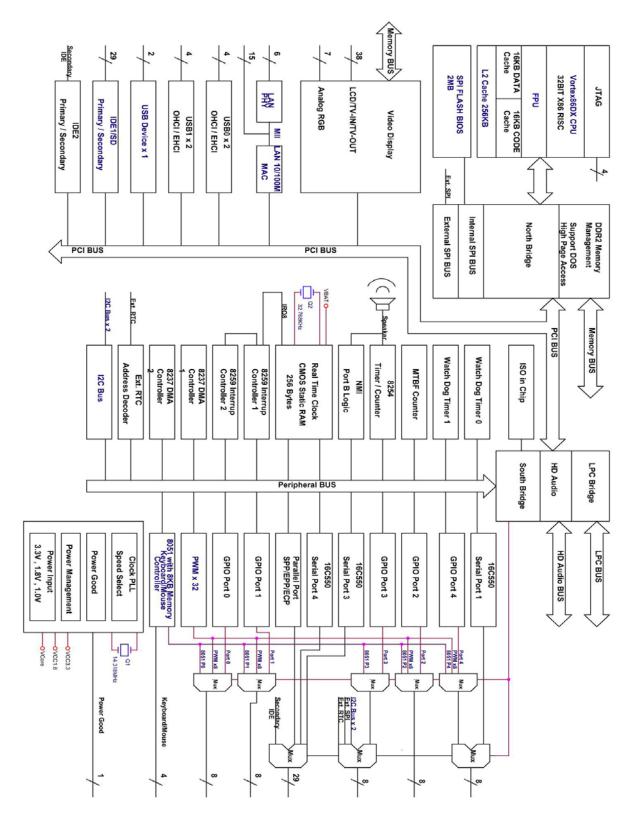

Detailed scheme of Vortex86MX connections

Have to note those in detailed schemes are **not** externally accessible Parallel port and GPIO Port 2.

#### **4. VCC**

User can feed devices connected on GPIO port through pin VCC with voltage of 5V. However there should be considered their limitations.

VCC pin has in circuit PTC fuse which limits current from this output. Maximal continuous current is **1,1A** (**5,5W**). For short period is allowed to feed 1,3A. When device feeds more than 1,3A then PTC device starts to trip into high impedance state. Trip time is about 0,3s @ 8A. Maximal current which can PTC withstand without damage is 40A.

## 5. GPIO – General Purpose Input Output ports

GPIO ports are commonly used for relatively slow data acquisitions or for signaling external devices. On devices all GPIO pins are independent and can be configured as inputs or outputs, with or without pull-up/pull-down resistors.

#### 5.1. Pinout

GPIO port #0, #1 are shared with PWM #0, #1 GPIO port #3 is shared with SPI and I2C ports

Numbering of pins is from down to top and left to right when looking on open connector from outside. GPIO group #0: pin 4,6,8,10,12,14,16,17 in order 0.-7. bit GPIO group #1: pin 3,5,7,9,11,13,15,17 in order 0.-7. bit GPIO group #3: pin 20,22,24,26,19,21,23,25 in order 0.-7. bit

| 26-pin, 2.54mm, 2 row |             |      |             |  |  |  |  |  |  |  |  |  |

|-----------------------|-------------|------|-------------|--|--|--|--|--|--|--|--|--|

| Pin#                  | Signal Name | Pin# | Signal Name |  |  |  |  |  |  |  |  |  |

| 1                     | VCC         | 2    | GND         |  |  |  |  |  |  |  |  |  |

| 3                     | GP10        | 4    | GP00        |  |  |  |  |  |  |  |  |  |

| 5                     | GP11        | 6    | GP01        |  |  |  |  |  |  |  |  |  |

| 7                     | GP12        | 8    | GP02        |  |  |  |  |  |  |  |  |  |

| 9                     | GP13        | 10   | GP03        |  |  |  |  |  |  |  |  |  |

| 11                    | GP14        | 12   | GP04        |  |  |  |  |  |  |  |  |  |

| 13                    | GP15        | 14   | GP05        |  |  |  |  |  |  |  |  |  |

| 15                    | GP16        | 16   | GP06        |  |  |  |  |  |  |  |  |  |

| 17                    | GP17        | 18   | GP07        |  |  |  |  |  |  |  |  |  |

| 19                    | GP34        | 20   | GP30        |  |  |  |  |  |  |  |  |  |

| 21                    | GP35        | 22   | GP31        |  |  |  |  |  |  |  |  |  |

| 23                    | GP36        | 24   | GP32        |  |  |  |  |  |  |  |  |  |

| 25                    | GP37        | 26   | GP33        |  |  |  |  |  |  |  |  |  |

| Pin description, box header on front panel |

|--------------------------------------------|

| 26-pin, 2.54mm, 2 row                      |

#### 5.2. Electrical characteristics

#### GPIO in output mode can drive 16mA.

GPIO in input mode are unterminated and are pulled-high by 75kOhm resistor.

Note:

For testing purposes you can easily check state in which ports are. Typically if are in output state you will measure 0V or 3.3V. In input state will measure 2.5V

#### 5.3. Programming

Description of programming GPIO ports provided in sample codes.

|                       | Port<br>#0 | Port<br>#1 | Port<br>#2 | Port<br>#3 | Port<br>#4 | Description                                             |

|-----------------------|------------|------------|------------|------------|------------|---------------------------------------------------------|

| Data Register         | 78H        | 79H        | 7AH        | 7BH        | 7CH        |                                                         |

| Direction<br>Register | 98H        | 99H        | 9AH        | 9BH        | 9CH        | 0: GPIO pin is input mode<br>1: GPIO pin is output mode |

Here is GPIO summary for direction and data registers:

If send value 0FH to port 98H, it means that GPIO port0 [7-4] are input mode and port[3-0] are output mode. If send value 00H to port 98H, it means that GPIO port0 [7-0] are input mode.

If send value FFH to port 98H, it means that GPIO port0 [7-0] are output mode.

If send value 03H to port 98H, it means that GPIO port0 [7-2] are input mode and port[1-0] are output mode.

#### 5.4. GPIO vs. BIOS Setup

GPIO port modes can be re-setup in program code by direct writing into PCI registers. If this setup is not done then is valid what is setup in BIOS. So if the pin is setup by BIOS into I2C mode then will ignore GPIO write/reads.

Recommend to see Appendix A - Technical Reference

#### 5.5. Performance

Tested maximum possible frequency of switching of GPIO ports using software loop which is doing just on/off operation on GPIO ports under Linux (Debian 6.0) and DOS (FreeDOS 1.1) is period approximately 550kHz. Is necessary to note that such period is unstable and fluctuate 340-600kHz.

Should be noted that for reading GPIO ports there is commonly possible to use interrupt. Port can have delay of time on which signal must be presented on GPIO to be interrupt initiated. The range of time is from 2ms to 100ms. Signal can be defined if should be high or low.

## 6. SPI – Serial Peripheral Interface bus

SPI ports are commonly used for fast data acquisitions from others integrated circuits. It is ideal interface to be connected on external ADC, DAC and other devices.

SPI interface discussed in this chapter is hardware controlled. Please do not mix with software emulated SPI interface (much slower).

## 6.1. Characteristics

SPI interface is intended only for high speed devices and is half duplex mode only. Has maximum speed 150Mbps, minimum speed 10Mbps.

Support only two clock modes: CPOL = 0, CPHA = 0CPOL = 1, CPHA = 0

Good description for modes http://en.wikipedia.org/wiki/Serial\_Peripheral\_Interface\_Bus

Clock modes are: 18750kHz, 15000kHz, 12500kHz, 10000kHz, 10714kHz, 11538kHz, 13636kHz, 16666kHz 21400kHz, 25000kHz, 30000kHz, 37000kHz, 50000kHz, 75000kHz, 150000kHz. Clock 21.4MHz counted as default.

#### 6.2. Pinout

SPI is shared with GPIO group #3. SPI is using pin 20,22,24,26.

## SPI interface SS (ENABLE), CLOCK (SCK), MOSI (SDO), MISO (SDI)

Signals are: pin 20: SS (ENABLE) pin 22: CLOCK (SCK) pin 24: MOSI (SDO) pin 26: MISO (SDI)

pin 2: common GND

## 6.3. Programming

Description of programming SPI is provided in sample codes and by libraries.

Recommend to see Appendix A - Technical Reference with registry description.

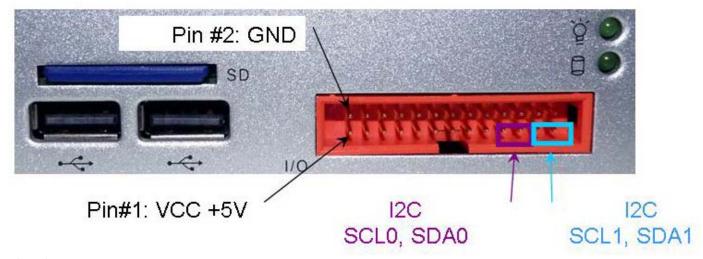

## 7. I2C – Inter integrated Circuit interface

I2C is typically used for connection of low and medium speed peripheral devices using two wire bus.

## 7.1. Characteristics

I2C interface in device support both master and slave modes. Support 10bit address (master only).

Support all speed modes

- standard mode (up to 100 kbps)

- fast mode (up to 400 kbps)

- high-speed mode (up to 3.3 Mbps)

Note that speed setup can be any speed up to 3.3Mbps, there are not fixed speed steps.

## 7.2. Pinout

I2C interfaces are shared with GPIO group #3.

I2C group #0 is using pin 19,21.

I2C group #1 is using pin 23,25.

Signals are: pin 19: SCL0 pin 21: SDA0 pin 23: SCL1 pin 25: SDA1

pin 2: common GND

## 7.3. Programming

Description of programming I2C is provided in sample codes and by libraries. Special notice should be taken for devices which are addressed 10bit or 7bit.

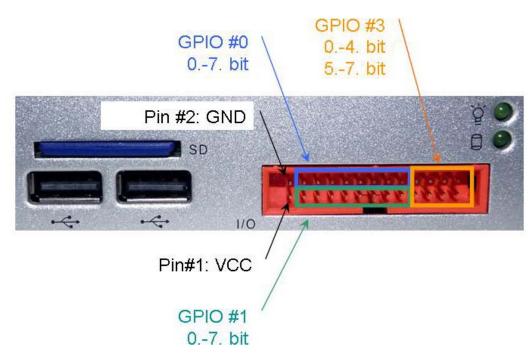

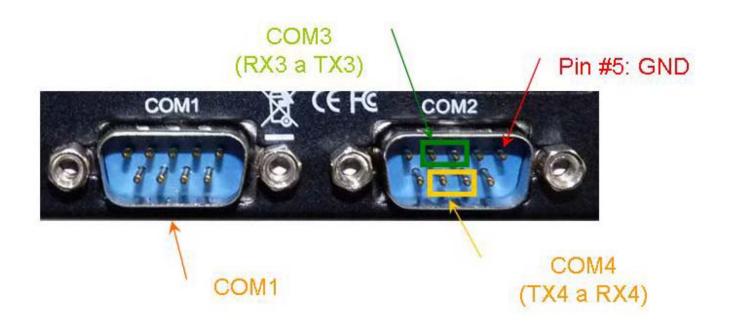

## 8. Serial ports

Serial ports COM1, COM3 and COM4 can be used as standard COM ports in Windows, Linux and DOS.

## 8.1. Characteristics

Serial ports in devices are in back panel.

Port COM1 is labeled connector "COM1". It is standard signals COM1 port on connector DB9. This port can be uased fully as standard COM port, f.e. for RS-232 connection of serial modems.

Port COM3 and COM4 are both on connector labeled "COM2". They have only signal RX and TX available. This port can be used only for devices which do not need controlling signals. Typical applications are UART interfaces.

User's can modify in BIOS all parameters of ports: IRQ, I/O base address and default speed.

Ports have speed from 2400-115200 as standard speed. It has also boosted speeds 31 200 - 748 800 bps.

Please note:

Ports can be RS-232, RS-422 or RS-485 type. However his type is given by model and regardless of setup in BIOS. So if user will setup device which is RS-232 as RS-485 port, it will anyway stays and will work as RS-232.

#### 8.2. Pinout

Connector DB9 (9pin) labeled as "COM1" COM1: Pin 1: DCD for RS-232 / TX- for RS-422 / Negative for RS-485 Pin 2: RxD for RS-232 / TX+ for RS-422 / Positive for RS-485 Pin 3: TxD for RS-232 / RX+ for RS-422 Pin 4: DTR for RS-232 / RX- for RS-422 Pin 5: GND Pin 6: DSR for RS-232 Pin 7: RTS for RS-232 Pin 8: CTS for RS-232 Pin 9: RI

Connector DB9 (9pin) labeled as "COM2"

COM3: Pin 2 RxD Pin 3 TxD

COM4: Pin 8 RxD Pin 7 TxD

Common: Pin 5 GND

Note: pinout is designed in such way that if not COM4 used there is not necessary to change piut of connection cable.

#### 8.3. Programming

Ports can be used as standard ports without special programming. Anyway also sample codes and libraries provided.

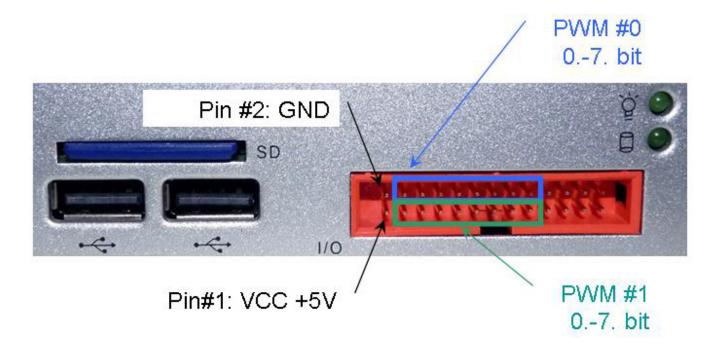

## 9. PWM - Pulse Width Modulation

PWM ports are typical used for controlling of power switches for stepper motors and servos. They could be also used for communication devices or communication interface emulations.

#### 9.1. Pinout

PWM #0, #1 are shared with GPIO #0, #1

#### 9.2. Electrical characteristics

PWM port can drive **16mA**. Value can be tuned from 4mA to16mA by programming PCI registers. 16mA is default value.

#### 9.3. Performance

Resolution of PWM self is up to **20ns** (50MHz clock of counter). PWM is hardware feature and works independently of CPU load. When applied with servos and libraries mentioned later can control feedback pulses +/- 1us.

PWM is possible to be programmed for exact number of pulses (counting mode) or into continual method. If in counting mode then is possible to check end of sequence and to program by software other sequence. Time to detect near-end of counting and start new sequence is about 8us (Linux Debian).

External interfaces Vortex86MX series

End of counting sequence is possible to detect by three methods:

- 1. use interrupt end of counting will call interrupt service procedure

- 2. by polling the Interrupt Status Register to check if interrupt should come

- 3. by polling the Registry Counter field in Control Register to check how many counts to end pending

## 9.4. Programming

Description of programming PWM is provided in sample codes and by libraries. There are available samples and libraries for direct PWM usage as low level function. Additionally there are libraries allows usage PWM for servos control with already prepared libraries for intelligent servo controls.

For better understanding is recommended to study documents related to "Intel 8254 programmable interval timer" and Appendix A - Technical Reference

## 10. Microcontroller 8051 notice

The SoC have also microcontroller 8051 inside. However this is undocumented possibility in device. User can met that setting is shared in BIOS with GPIO. Currently none documentation is provided or planed to be provided.

## 11. Software libraries

Most comprehensive software libraries for this device counts development for Roboard platform. This platform is designed by SoC's authors and is specialized for robotics's applications. Because most components and architecture is identical then such libraries are applicable directly or with very little modifications.

Home page of project <u>http://www.roboard.com/</u>

We should note that hardware (RB-100, RB110 etc.) for this project can be also sourced from us. Even user have took in consideration that those equipment is considered for a bit different application. It means there is not embedded VGA, no case etc.

## 11.1. RoBolO library

Whole project is build around RoBOIO library and has those above all significant points:

- open-source library

- free for academic & commercial use

- everyone is permitted to redistribute and/or modify it without restriction

Popular OS supported, library is cross-platformed

- Linux

- Windows XP

- Windows CE 6.0

- DOS

Wrappers for development libraries available

- .NET (C# and VB.NET) for .NET Framework 2.0 & above

- Visual Basic 6.0

- Borland C++ Builder

- JAVA for Windows XP

- Python for Windows XP

Currently (version 1.8) supported I/O functions which are directly applicable with discussed devices

- GPIO

- PWM

- SPI hardware

- I2C hardware

- COM (RS-232, RS-485, TTL)

Additionally there libraries which gives very good idea for own project, they could be used directly or are very good for inspirations of own projects

• SPI software emulated for slow SPI equipment

External interfaces Vortex86MX series

- I2C software emulated for nonstandard device

- A/D complete libraries for connection on ADC circuit by Analog AD79x8 family on SPI

- RC servo control for many servos (KONDO, HiTEC,....)

- Easier integration for sensors and information for real applications of

- A/D, SPI, I2C: accelerometer, gyroscope, ...

- o COM: GPS, AI servos, ...

- o PWM: RC servos, DC motors, ...

- o GPIO: bumper, infrared sensors, on/off switches, ...

- o USB: webcam, ...

- o Audio in/out: speech interfaces

For developers there is big advantage thanks wide range of tools they can freely use, because platform is x86 based and almost all resources on PC can be employed as development tools

- Languages: C/C++/C#, Visual Basic, Java, Python, LabVIEW

- Libraries: OpenCV, SDL, LAPACK

- IDE: Visual Studio, DevVisual Dev--C++, Eclipse

- GUI: Windows Forms, GTK

#### 11.2. How to use

From home page of project <u>http://www.roboard.com/</u> is recommend to download latest versions. Is very good idea to read introduction documents. Highly recommended document which gives overview is **"RoBoIO 1.8 Introducion Slide"**

Then download libraries and related to planed OS. Is recommended to follow guides attached to libraries and recompile them for your OS.

After successful compilation for your OS is necessary to modify one or two file to allow full operations of libraries on discussed platform.

#### A]

In fact will enough to switch-off Roboard platform checks. For this case developers already prepared code and in code is parameter ROBOIO. Unfortunately at least in version 1.8 code not completely clean up so there are two ways how to customize code for your platform.

in file ROBOIO/libsrc/define.h remove line *#define ROBOIO (0x0181)* or do same using parameter for compiler.

This will be completely ok if code is cleaned up and it will allow to skip codes sections which verifying if hardware is exactly RoBoard. Unfortunately is not, so during compilation you will met procedures which claimes for missing *roboio\_GetRBVersion()*. This is then easily solved using section

#ifdef ROBOIO

#### #endif

...

Please check in file ROBOIO/libsrc/i2c.cpp modify those functions: i2cResetPin(void) and i2cClearResetPin(void)

#ifdef ROBOIO

if (roboio\_GetRBVer()!= .....) {... return false};

#endif

Please check in file ROBOIO/libsrc/spi.cpp modify those functions: spi\_DisableSS(void) and spi\_EnableSSn(void)

#ifdef ROBOIO

if (roboio\_GetRBVer()!= .....) {... return false};

#endif

Please note that this patch has drawback – all samples written then in package RoboKit counts with ROBOIO define, so will claim for functions related with this define. Maybe faster for first usage of library is to use a bit ugly patch mentioned in variant B]

B]

This kind of patch modifies source coude such way that you will then declared your Vortex86DX or MX board as RB100 for RoboIO libraries. Advantage is that you can use for future regulary sample files even they are written for Roboard without any modifications.

Please check in file ROBOIO/libsrc/common.cpp modify those functions: Roboio\_CheckRBVer(void) find line *if* (*cpu\_id* == *CPU\_VORTEX\_DX\_1*) *return true;* and add after him line *if* (*cpu\_id* == *CPU\_VORTEX\_MX*) *return true if* (*cpu\_id* == *CPU\_VORTEX\_MX*) *return true*;

Please check in file ROBOIO/libsrc/io.cpp modify those function: Io\_init(void) find line which content following condition *if* ((*io\_CpuID*() != *CPU\_VORTEX\_DX\_1*) && (*io\_CpuID*() != *CPU\_VORTEX\_DX\_2*) && (*io\_CpuID*() != *CPU\_VORTEX\_DX\_3*))

and modify them to accept also CPU\_VORTEX\_MX and CPU\_VORTEX\_MX\_PLUS

*if* ((*io\_CpuID*() != *CPU\_VORTEX\_DX\_1*) && (*io\_CpuID*() != *CPU\_VORTEX\_DX\_2*) && (*io\_CpuID*() != *CPU\_VORTEX\_DX\_3*) && (*io\_CpuID*() != *CPU\_VORTEX\_MX*) && (*io\_CpuID*() != *CPU\_VORTEX\_MX\_PLUS*))

With this patch you can call libraries and claim them that you have *RB100* board. You can compile sample programs from RoboKit and try their functionalities immediately on your platform.

Note that patch A] and patch B] does not collide.

# 12. Appendix A - Technical Reference

Description of Vortex86DX and Vortex86MX series registers.

## **1. PCI Configuration Registers**

| I/O Port:      | CF8h – Accessed as a Dword         |

|----------------|------------------------------------|

| Register Name: | PCI Configuration Address Register |

| Reset Value:   | 0000000h                           |

| 31     | 30 | 29 | 28 | 27  | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1  | 0  |

|--------|----|----|----|-----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|----|----|

| C<br>E |    |    | ł  | Rsv | d  |    |    |    |    |    | В  | N  |    |    |    |    |    | DN |    |    |    | FN |   |   |   | R | N |   |   | Rs | vd |

Configuration Address Register is a 32-bit register accessed only when referenced as a DWORD. A byte or word reference will pass through the Configuration Address Register onto the PCI bus as an I/O cycle.

| Bit   | Name | Attribute | Description                                                                                |

|-------|------|-----------|--------------------------------------------------------------------------------------------|

|       |      |           | Configuration Enable.                                                                      |

| 31    | CE   | R/W       | When this bit is set to 1, accesses to PCI configuration space are enabled. If this bit is |

|       |      |           | reset to 0, accesses to PCI configuration space are disabled.                              |

| 30-24 | Rsvd | RO        | Reserved.                                                                                  |

|       |      |           | Bus Number.                                                                                |

|       |      |           | When the bus number is programmed to 00h, the target of the configuration cycle is         |

|       |      |           | either the North-Bridge or the PCI Device that is connected to the North-Bridge. If the    |

| 23-16 | BN   | R/W       | bus number is programmed to 00h and the North-Bridge is not the target, a Type 0           |

|       |      |           | configuration cycle is generated on PCI Bus. IF the bus number is non-zero, a Type 1       |

|       |      |           | configuration cycle is generated on PCI bus with the bus number mapped to AD[23:16]        |

|       |      |           | during the address phase.                                                                  |

|       |      |           | Device Number.                                                                             |

| 15-11 | DN   | R/W       | This field selects one agent on the PCI bus. During a Type 1 configuration cycle, this     |

| 13-11 | DIN  | 17/17     | field is mapped to AD[15:11]. During a Type 0 configuration cycle, this field is decoded   |

|       |      |           | and one of AD[31:11] is driven to 1.                                                       |

|       |      |           | Function Number.                                                                           |

| 10-8  | FN   | R/W       | This field allows the configuration registers of a particular function in a multi-function |

| 10-0  |      | 1.7.4.4   | device to be accessed. The Vortex86DX North Bridge only responds to configuration          |

|       |      |           | cycle with a function number of 000b.                                                      |

|       |      |           | Register Number.                                                                           |

| 7-2   | RN   | R/W       | This field selects one register within a particular Bus, Device, and Function as specified |

|       |      |           | by the other fields in the Configuration Address Register.                                 |

| 1-0   | Rsvd | RO        | Reserved.                                                                                  |

| I/O Port:        | FCh – Accessed as a Dword                                                            |  |  |  |  |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

| Register Name:   | PCI Configuration Data Register                                                      |  |  |  |  |  |  |  |  |  |  |  |

| Reset Value:     | 0000000h                                                                             |  |  |  |  |  |  |  |  |  |  |  |

| 31 30 29 28 27 2 | 1 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |  |  |  |  |  |  |  |  |  |  |  |

|                  | CDR                                                                                  |  |  |  |  |  |  |  |  |  |  |  |

Configuration Data Register is a 32-bit read/write window into configuration space. The portion of configuration space that is referenced by Configuration Data Register is determined by the contents of Configuration Address Register.

| Bit  | Name | Attribute | Description                                                                               |

|------|------|-----------|-------------------------------------------------------------------------------------------|

|      |      |           | If bit 31 of PCI Configuration Address Register is 1, any I/O reference that falls in the |

| 31-0 | CDR  | R/W       | PCI Configuration Data Register space is mapped to configuration space using the          |

|      |      |           | contents of PCI Configuration Address Register.                                           |

## 2.1.GPIO

40 GPIO pins are provided by the Vortex86DX/MX for general usage in the system. All GPIO pins are independent and can be configured as inputs our outputs; when configured as outputs, pins have 16 mA drive capability and are unterminated; when configured as inputs, pins are pulled-high with a 75k ohm resistance.

GPIO port 0,1 and 2 are always free for use normally. In your system is possible that some GPIO group is not externaly connected.

See further Internal Peripheral Feature Control Register in chapter Servo Registry for description how to control GPIO availability.

#### **Setup GPIO Direction**

|                    | Port 0 | Port 1 | Port 2 | Port 3 | Port 4 | Description                |

|--------------------|--------|--------|--------|--------|--------|----------------------------|

| Data Register      | 78H    | 79H    | 7AH    | 7BH    | 7CH    |                            |

| Direction Register | 98H    | 99H    | 9AH    | 9BH    | 9CH    | 0: GPIO pin is input mode  |

|                    |        |        |        |        |        | 1: GPIO pin is output mode |

Here is GPIO direction and data registers:

If send value 0FH to port 98H, it means that GPIO port0 [7-4] are input mode and port[3-0] are output mode.

If send value 00H to port 98H, it means that GPIO port0 [7-0] are input mode.

If send value FFH to port 98H, it means that GPIO port0 [7-0] are output mode.

If send value 03H to port 98H, it means that GPIO port0 [7-2] are input mode and port[1-0] are output mode.

## 2.2. GPIO with Interrupt

GPIO port 0 & 1 in Vortex86DX support interrupt trigger. Programmers can use interrupt to instead of polling GPIO to save CPU performance. GPIO port0 interrupt registers are at offset DCh~DFh in PCI south bridge and GPIO1 registers are at offset E0h~E3h.

Here are steps to setup GPIO to trigger interrupt:

1. Configure interrupt mask register to determine which GPIO can trigger interrupt individually.

2. Set trigger level (high or low) for each GPIO.

3. Set period time that interrupt will be generated while the event loading time of any one of GPIO[7-0] is longer than the time parameters.

4. Select IRQ.

5. Set interrupt trigger once or continuously.

# 2.3. GPIO Interrupt Relative Registers

| Register Offset: |   |   |     | DCh    |      |          |        |         |    |

|------------------|---|---|-----|--------|------|----------|--------|---------|----|

| Register Name:   |   |   |     | GPIO P | ORT0 | Interrup | t Mask | Registe | ۶r |

| Reset Value:     |   |   | 00h |        |      |          |        |         |    |

|                  | 7 | 6 | 5   | 4      | 3    | 2        | 1      | 0       |    |

|                  |   |   |     | POI    | MTM  |          |        |         |    |

| Bit | Name    | Attribute | Description                                                                                 |

|-----|---------|-----------|---------------------------------------------------------------------------------------------|

|     |         |           | GPIO PORT0 Interrupt Mask Register: This mask register is workable when Port0[x] is         |

|     |         | INTM R/W  | at input or output mode. If Port0[x] is at output mode and interrupt level set as high, the |

| 7-0 |         |           | interrupt will occur base on the GPIO_PORT0 interrupt control register.                     |

| 7-0 | FUINTIN |           | Bit0 for Port0[0], Bit1 for Port0[1],, Bit7 for Port0[7]                                    |

|     |         |           | 1: Enable Interrupt happen                                                                  |

|     |         |           | 0: Disable interrupt                                                                        |

| Registe      | r Offse | et: | DDh    |      |          |         |          |

|--------------|---------|-----|--------|------|----------|---------|----------|

| Registe      | r Namo  | e:  | GPIO P | ORT0 | Interrup | t Level | Register |

| Reset Value: |         |     | FFh    |      |          |         |          |

| 7 6 5        |         |     | 4      | 3    | 2        | 1       | 0        |

|              |         |     | P0I    | NTL  |          |         |          |

| Bit | Name   | Attribute | escription                                               |  |  |  |  |

|-----|--------|-----------|----------------------------------------------------------|--|--|--|--|

|     |        |           | GPIO PORT0 Interrupt Level Register                      |  |  |  |  |

| 7-0 |        | R/W       | Bit0 for Port0[0], Bit1 for Port0[1],, Bit7 for Port0[7] |  |  |  |  |

| 7-0 | POINTL | r///      | 1: Interrupt activated on Port0 low level                |  |  |  |  |

|     |        |           | 0: Interrupt activated on Port0 high level               |  |  |  |  |

| F              | Registe | r Offse | et: | DEh    |      |          |         |         |      |

|----------------|---------|---------|-----|--------|------|----------|---------|---------|------|

| Register Name: |         |         |     | GPIO P | ORT0 | Interrup | t Contr | ol Regi | ster |

| Reset Value:   |         |         | 00h |        |      |          |         |         |      |

|                | 7       | 7 6 5   |     | 4      | 3    | 2        | 1       | 0       |      |

| En IKP         |         |         |     |        | POI  | NTR      |         |         |      |

| Bit | Name | Attribute | Description                               |

|-----|------|-----------|-------------------------------------------|

| 7   | En   | R/W       | GPIO PORT0 Interrupt Function Enable bit. |

| 1   |      | r/w       | 0: Disable (Default)                      |

| Bit | Name   | Attribute | scription                                                                                   |  |  |  |  |  |  |

|-----|--------|-----------|---------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|     |        |           | nable                                                                                       |  |  |  |  |  |  |

|     |        |           | Interrupt Keep Period.                                                                      |  |  |  |  |  |  |

|     |        |           | Interrupt will be generated while the event loading time of any one of port0[7-0] is longer |  |  |  |  |  |  |

|     |        |           | than the following time parameters . Reference 14.318MHz                                    |  |  |  |  |  |  |

|     |        |           | 000: 002ms                                                                                  |  |  |  |  |  |  |

|     |        |           | 001: 005ms                                                                                  |  |  |  |  |  |  |

| 6-4 | IKP    | R/W       | 010: 010ms                                                                                  |  |  |  |  |  |  |

|     |        |           | 011: 020ms                                                                                  |  |  |  |  |  |  |

|     |        |           | 100: 040ms                                                                                  |  |  |  |  |  |  |

|     |        |           | 101: 060ms                                                                                  |  |  |  |  |  |  |

|     |        |           | 110: 080ms                                                                                  |  |  |  |  |  |  |

|     |        |           | 111: 100ms                                                                                  |  |  |  |  |  |  |

|     |        |           | GPIO PORT0 Interrupt Routing Register                                                       |  |  |  |  |  |  |

|     |        |           | <u>Bit 11 Bit 10 Bit 9 Bit 8</u> Routing Table                                              |  |  |  |  |  |  |

|     |        |           | 0 0 0 Disable.                                                                              |  |  |  |  |  |  |

|     |        |           | 0 0 0 1 IRQ[9]                                                                              |  |  |  |  |  |  |

|     |        |           | 0 0 1 0 IRQ[3]                                                                              |  |  |  |  |  |  |

|     |        |           | 0 0 1 1 IRQ[10]                                                                             |  |  |  |  |  |  |

|     |        |           | 0 1 0 0 IRQ[4]                                                                              |  |  |  |  |  |  |

|     |        |           | 0 1 0 1 IRQ[5]                                                                              |  |  |  |  |  |  |

| 3-0 | POINTR | R/W       | 0 1 1 0 IRQ[7]                                                                              |  |  |  |  |  |  |

|     |        |           | 0 1 1 1 IRQ[6]                                                                              |  |  |  |  |  |  |

|     |        |           | 1 0 0 0 IRQ[1]                                                                              |  |  |  |  |  |  |

|     |        |           | 1 0 0 1 IRQ[11]                                                                             |  |  |  |  |  |  |

|     |        |           | 1 0 1 0 Reserved                                                                            |  |  |  |  |  |  |

|     |        |           | 1 0 1 1 IRQ[12]                                                                             |  |  |  |  |  |  |

|     |        |           | 1 1 0 0 Reserved<br>1 1 0 1 IRQ[14]                                                         |  |  |  |  |  |  |

|     |        |           | 1 1 1 0 Reserved                                                                            |  |  |  |  |  |  |

|     |        |           |                                                                                             |  |  |  |  |  |  |

|     |        |           | 1 1 1 IRQ[15]                                                                               |  |  |  |  |  |  |

| Registe        | er Offse | et: | DFh    |      |          |        |        |             |

|----------------|----------|-----|--------|------|----------|--------|--------|-------------|

| Register Name: |          |     | GPIO P | ORT0 | Interrup | t Mode | Contro | ol Register |

| Reset V        | /alue:   |     | 00h    |      |          |        |        |             |

| 7              | 6        | 5   | 4      | 3    | 2        | 1      | 0      |             |

|                |          |     | P0IN   | TCTL |          |        |        |             |

| Bit | Name     | Attribute | Description                           |

|-----|----------|-----------|---------------------------------------|

| 7-0 | POINTCTL | R/W       | GPIO PORT0 Interrupt Control Register |

|  | Bit0 for Port0[0], Bit1 for Port0[1],, Bit7 for Port0[7]                                    |

|--|---------------------------------------------------------------------------------------------|

|  | 1: trigger the interrupt continuously if level is activated and match interrupt keep period |

|  | settings.                                                                                   |

|  | 0: Trigger the Interrupt once if level is activated.                                        |

| Registe      | er Offse | et: | E0h    |      |          |        |          |

|--------------|----------|-----|--------|------|----------|--------|----------|

| Registe      | er Name  | e:  | GPIO F | ORT1 | Interrup | t Mask | Register |

| Reset Value: |          |     | 00h    |      |          |        |          |

| 7            | 6        | 5   | 4      | 3    | 2        | 1      | 0        |

|              |          |     | P1II   | NTM  |          |        |          |

| Bit | Name   | Attribute | Description                                                                                                                                                                                                                                             |

|-----|--------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0 | P INTM | R/W       | GPIO PORT1 Interrupt Mask Register: This mask register is workable when Port1[x] is at input or output mode. If Port1[x] is at output mode and interrupt level set to high, the interrupt will occur base on the GPIO_PORT1 interrupt control register. |

|     |        |           | Bit0 for Port1[0], Bit1 for Port1[1],, Bit7 for Port1[7]<br>1: Enable Interrupt happen<br>0: Disable interrupt                                                                                                                                          |

| Register Offset: |        |   | E1h    |      |         |         |         |    |

|------------------|--------|---|--------|------|---------|---------|---------|----|

| Register Name:   |        |   | GPIO P | ORT1 | nterrup | t Level | Registe | ۶r |

| Reset V          | /alue: |   | FFh    |      |         |         |         |    |

| 7                | 6      | 5 | 4      | 3    | 2       | 1       | 0       |    |

|                  |        |   |        | NTL  |         |         |         |    |

| Bit | Name       | Attribute                           | Description                                              |

|-----|------------|-------------------------------------|----------------------------------------------------------|

|     | P1INTL R/W | GPIO PORT1 Interrupt Level Register |                                                          |

| 7.0 |            | ITL R/W                             | Bit0 for Port1[0], Bit1 for Port1[1],, Bit7 for Port1[7] |

| 7-0 |            |                                     | 1: Interrupt activated on Port1 low level                |

|     |            |                                     | 0: Interrupt activated on Port1 high level               |

| Register Offset: |        |     |        | E2h  |          |         |          |      |  |

|------------------|--------|-----|--------|------|----------|---------|----------|------|--|

| Register Name:   |        |     | GPIO P | ORT1 | Interrup | t Contr | ol Regis | ster |  |

| Reset Value:     |        | 00h |        |      |          |         |          |      |  |

|                  | 7      | 6   | 5      | 4    | 3        | 2       | 1        | 0    |  |

|                  | En IKP |     |        |      | P1II     | NTR     |          |      |  |

| Bit | Name   | Attribute | Description                                                                                 |  |  |  |

|-----|--------|-----------|---------------------------------------------------------------------------------------------|--|--|--|

|     |        |           | GPIO PORT1 Interrupt Function Enable bit.                                                   |  |  |  |

| 7   | En     | R/W       | 0: Disable (Default)                                                                        |  |  |  |

|     |        |           | 1: Enable                                                                                   |  |  |  |

|     |        |           | Interrupt Keep Period.                                                                      |  |  |  |

|     |        |           | Interrupt will be generated while the event loading time of any one of port0[7-0] is longer |  |  |  |

|     |        |           | than the following time parameters .                                                        |  |  |  |

|     |        |           | Reference 14.318MHz                                                                         |  |  |  |

|     |        |           | 000: 002ms                                                                                  |  |  |  |

| 6-4 | IKP    | R/W       | 001: 005ms                                                                                  |  |  |  |

| 0-4 |        | 1.7/ V V  | 010: 010ms                                                                                  |  |  |  |

|     |        |           | 011: 020ms                                                                                  |  |  |  |

|     |        |           | 100: 040ms                                                                                  |  |  |  |

|     |        |           | 101: 060ms                                                                                  |  |  |  |

|     |        |           | 110: 080ms                                                                                  |  |  |  |

|     |        |           | 111: 100ms                                                                                  |  |  |  |

|     |        |           | GPIO PORT1 Interrupt Routing Register                                                       |  |  |  |

|     |        |           | <u>Bit 11</u> Bit 10 Bit 9 Bit 8 Routing Table                                              |  |  |  |

|     |        |           | 0 0 0 Disable.                                                                              |  |  |  |

|     |        |           | 0 0 0 1 IRQ[9]                                                                              |  |  |  |

|     |        |           | 0 0 1 0 IRQ[3]                                                                              |  |  |  |

|     |        |           | 0 0 1 1 IRQ[10]                                                                             |  |  |  |

|     |        |           | 0 1 0 0 IRQ[4]                                                                              |  |  |  |

|     |        |           | 0 1 0 1 IRQ[5]                                                                              |  |  |  |

| 3-0 | P1INTR | R/W       | 0 1 1 0 IRQ[7]                                                                              |  |  |  |

|     |        |           | 0 1 1 1 IRQ[6]                                                                              |  |  |  |

|     |        |           | 1 0 0 0 IRQ[1]                                                                              |  |  |  |

|     |        |           | 1 0 0 1 IRQ[11]                                                                             |  |  |  |

|     |        |           | 1 0 1 0 Reserved                                                                            |  |  |  |

|     |        |           | 1 0 1 1 IRQ[12]                                                                             |  |  |  |

|     |        |           | 1 1 0 0 Reserved                                                                            |  |  |  |

|     |        |           | 1 1 0 1 IRQ[14]                                                                             |  |  |  |

|     |        |           |                                                                                             |  |  |  |

|     |        |           | 1 1 1 IRQ[15]                                                                               |  |  |  |

| Registe | er Offse | et: | E3h    |      |          |        |        |            |

|---------|----------|-----|--------|------|----------|--------|--------|------------|

| Registe | er Name  | e:  | GPIO P | ORT1 | Interrup | t Mode | Contro | l Register |

| Reset V | alue:    |     | 00h    |      |          |        |        |            |

| 7       | 6        | 5   | 4      | 3    | 2        | 1      | 0      |            |

|         |          |     | P1IN   | TCTL |          |        |        |            |

| Bit | Name     | Attribute | Description                                                                                 |

|-----|----------|-----------|---------------------------------------------------------------------------------------------|

|     |          |           | GPIO PORT1 Interrupt Control Register                                                       |

|     |          |           | Bit0 for Port1[0], Bit1 for Port1[1],, Bit7 for Port1[7]                                    |

| 7-0 | P1INTCTL | R/W       | 1: trigger the interrupt continuously if level is activated and match interrupt keep period |

|     |          |           | settings.                                                                                   |

|     |          |           | 0: Trigger the Interrupt once if level is activated.                                        |

# 3. Servo Registers

#### **SERVO Registers**

(Base Address Refers to the Register of index D3h-D0h, IDSEL = AD18/SB of PCI Configuration Register)

| IO Address | Register Name                      |

|------------|------------------------------------|

| BA + 00H   | SERVO Interrupt Mask Register      |

| BA + 04H   | SERVO Interrupt Status Register    |

| BA + 08H   | SERVO Sync Register                |

| BA + 0CH   | SERVO[0] Pulse Low Count Register  |

| BA + 10H   | SERVO[0] Pulse High Count Register |

| BA + 14H   | SERVO[0] Control Register          |

| BA + 18H   | SERVO[1] Pulse Low Count Register  |

| BA + 1CH   | SERVO[1] Pulse High Count Register |

| BA + 20H   | SERVO[1] Control Register          |

| BA + 24H   | SERVO[2] Pulse Low Count Register  |

| BA + 28H   | SERVO[2] Pulse High Count Register |

| BA + 2CH   | SERVO[2] Control Register          |

| BA + 30H   | SERVO[3] Pulse Low Count Register  |

| BA + 34H   | SERVO[3] Pulse High Count Register |

| BA + 38H   | SERVO[3] Control Register          |

| BA + 3CH   | SERVO[4] Pulse Low Count Register  |

| BA + 40H   | SERVO[4] Pulse High Count Register |

| BA + 44H   | SERVO[4] Control Register          |

| BA + 48H   | SERVO[5] Pulse Low Count Register  |

| BA + 4CH   | SERVO[5] Pulse High Count Register |

| BA + 50H   | SERVO[5] Control Register          |

| BA + 54H   | SERVO[6] Pulse Low Count Register  |

| BA + 58H   | SERVO[6] Pulse High Count Register |

| BA + 5CH   | SERVO[6] Control Register          |

| BA + 60H   | SERVO[7] Pulse Low Count Register  |

| BA + 64H   | SERVO[7] Pulse High Count Register |

| BA + 68H   | SERVO[7] Control Register          |

| BA + 6CH   | SERVO[8] Pulse Low Count Register  |

| BA + 70H   | SERVO[8] Pulse High Count Register |

| BA + 74H   | SERVO[8] Control Register          |

| BA + 78H   | SERVO[9] Pulse Low Count Register  |

| BA + 7CH   | SERVO[9] Pulse High Count Register |

| BA + 80H   | SERVO[9] Control Register          |

| BA + 84H   | SERVO[10] Pulse Low Count Register |

| IO Address | Register Name                       |

|------------|-------------------------------------|

| BA + 88H   | SERVO[10] Pulse High Count Register |

| BA + 8CH   | SERVO[10] Control Register          |

| BA + 90H   | SERVO[11] Pulse Low Count Register  |

| BA + 94H   | SERVO[11] Pulse High Count Register |

| BA + 98H   | SERVO[11] Control Register          |

| BA + 9CH   | SERVO[12] Pulse Low Count Register  |

| BA + A0H   | SERVO[12] Pulse High Count Register |

| BA + A4H   | SERVO[12] Control Register          |

| BA + A8H   | SERVO[13] Pulse Low Count Register  |

| BA + ACH   | SERVO[13] Pulse High Count Register |

| BA + B0H   | SERVO[13] Control Register          |

| BA + B4H   | SERVO[14] Pulse Low Count Register  |

| BA + B8H   | SERVO[14] Pulse High Count Register |

| BA + BCH   | SERVO[14] Control Register          |

| BA + C0H   | SERVO[15] Pulse Low Count Register  |

| BA + C4H   | SERVO[15] Pulse High Count Register |

| BA + C8H   | SERVO[15] Control Register          |

| BA + CCH   | SERVO[16] Pulse Low Count Register  |

| BA + D0H   | SERVO[16] Pulse High Count Register |

| BA + D4H   | SERVO[16] Control Register          |

| BA + D8H   | SERVO[17] Pulse Low Count Register  |

| BA + DCH   | SERVO[17] Pulse High Count Register |

| BA + E0H   | SERVO[17] Control Register          |

| BA + E4H   | SERVO[18] Pulse Low Count Register  |

| BA + E8H   | SERVO[18] Pulse High Count Register |

| BA + ECH   | SERVO[18] Control Register          |

| BA + F0H   | SERVO[19] Pulse Low Count Register  |

| BA + F4H   | SERVO[19] Pulse High Count Register |

| BA + F8H   | SERVO[19] Control Register          |

| BA + FCH   | SERVO[20] Pulse Low Count Register  |

| BA + 100H  | SERVO[20] Pulse High Count Register |

| BA + 104H  | SERVO[20] Control Register          |

| BA + 108H  | SERVO[21] Pulse Low Count Register  |

| BA + 10CH  | SERVO[21] Pulse High Count Register |

| BA + 110H  | SERVO[21] Control Register          |

| BA + 114H  | SERVO[22] Pulse Low Count Register  |

| BA + 118H  | SERVO[22] Pulse High Count Register |

| BA + 11CH  | SERVO[22] Control Register          |

| BA + 120H  | SERVO[23] Pulse Low Count Register  |

Technical Reference

| IO Address | Register Name                       |

|------------|-------------------------------------|

| BA + 124H  | SERVO[23] Pulse High Count Register |

| BA + 128H  | SERVO[23] Control Register          |

| BA + 12CH  | SERVO[24] Pulse Low Count Register  |

| BA + 130H  | SERVO[24] Pulse High Count Register |

| BA + 134H  | SERVO[24] Control Register          |

| BA + 138H  | SERVO[25] Pulse Low Count Register  |

| BA + 13CH  | SERVO[25] Pulse High Count Register |

| BA + 140H  | SERVO[25] Control Register          |

| BA + 144H  | SERVO[26] Pulse Low Count Register  |

| BA + 148H  | SERVO[26] Pulse High Count Register |

| BA + 14CH  | SERVO[26] Control Register          |

| BA + 150H  | SERVO[27] Pulse Low Count Register  |

| BA + 154H  | SERVO[27] Pulse High Count Register |

| BA + 158H  | SERVO[27] Control Register          |

| BA + 15CH  | SERVO[28] Pulse Low Count Register  |

| BA + 160H  | SERVO[28] Pulse High Count Register |

| BA + 164H  | SERVO[28] Control Register          |

| BA + 168H  | SERVO[29] Pulse Low Count Register  |

| BA + 16CH  | SERVO[29] Pulse High Count Register |

| BA + 170H  | SERVO[29] Control Register          |

| BA + 174H  | SERVO[30] Pulse Low Count Register  |

| BA + 178H  | SERVO[30] Pulse High Count Register |

| BA + 17CH  | SERVO[30] Control Register          |

| BA + 180H  | SERVO[31] Pulse Low Count Register  |

| BA + 184H  | SERVO[31] Pulse High Count Register |

| BA + 188H  | SERVO[31] Control Register          |

| I/O Port:         | BA + 00h                                                              |

|-------------------|-----------------------------------------------------------------------|

| Register Name:    | SERVO Interrupt Mask Register                                         |

| Reset Value:      | 0000000h                                                              |

| 31 30 29 28 27 26 | 6 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 |

SIM[31-0]

| Bit  | Name          | Attribute | Description                         |

|------|---------------|-----------|-------------------------------------|

|      |               |           | SERVO[31-0] Interrupt Mask Register |

| 31-0 | SIM[31-0] R/W | R/W       | 1: Enable Interrupt                 |

|      |               |           | 0: Disable Interrupt                |

I/O Port:BA + 04hRegister Name:SERVO Interrupt Status RegisterReset Value:0000000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SIS[31-0]

| Bit  | Name      | Attribute | Description                                |

|------|-----------|-----------|--------------------------------------------|

|      |           |           | SERVO[31-0] Interrupt Status Register      |

| 31-0 | SIS[31-0] | R/W       | 1: Interrupt happen and write "1" to clear |

|      |           |           | 0: No Interrupt                            |

| I/O Port:      | BA + 08h                   |

|----------------|----------------------------|

| Register Name: | SERVO Sync Status Register |

| Reset Value:   | 0000000h                   |

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

| SYNC | [31-0] |

|------|--------|

|------|--------|

| Bit  | Name       | Attribute | Description               |

|------|------------|-----------|---------------------------|

|      |            |           | SERVO[31-0] Sync Register |

| 31-0 | SYNC[31-0] | R/W       | 1: SERVO will be hold     |

|      |            |           | 0: SERVO without hold     |

I/O Port:

BA + 0CH, 18H, 24H, 30H, 3CH, 48H, 54H, 60H, 6CH, 78H, 84H, 90H, 9CH, A8H, B4H, C0H,

CCH, D8H, E4H, F0H, FCH, 108H, 114H, 120H, 12CH, 138H, 144H, 150H, 15CH, 168H, 174H,

180H

**Register Name:** SERVO Pulse Low Register

Reset Value: 0000000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SPL

| Bit  | Name | Attribute | Description                                    |

|------|------|-----------|------------------------------------------------|

| 31-0 | SPL  | R/W       | SERVO Pulse Low Register. SERVO clock is 10MHz |

I/O Port: BA + 10H, 1CH, 28H, 34H, 40H, 4CH, 58H, 64H, 70H, 7CH, 88H, 94H, A0H, ACH, B8H, C4H, D0H, DCH,

E8H, F4H,100H,10CH,118H,124H,130H,13CH,148H,154H,160H,16CH,178H,184H

Register Name: SERVO Pulse High Register

#### Reset Value: 0000000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

SPH

| Bit  | Name | Attribute | Description                                     |

|------|------|-----------|-------------------------------------------------|

| 31-0 | SPH  | R/W       | SERVO Pulse High Register. SERVO clock is 10MHz |

**I/O Port:** BA + 14H, 20H, 2CH, 38H, 44H, 50H, 5CH, 68H, 74H, 80H, 8CH, 98H, A4H, B0H, BCH, C8H, D4H, E0H, ECH, F8H, 104H, 110H, 11CH, 128H, 134H, 140H, 14CH, 158H, 164H, 170H, 17CH, 188H

Register Name: SERVO Control Register

Reset Value: 0000000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

| RC RC |  |

|-------|--|

|-------|--|

| Bit  | Name | Attribute | Description                                                 |

|------|------|-----------|-------------------------------------------------------------|

|      |      |           | SERVOx Enable Control                                       |

| 31   | SE   | R/W       | 1: SERVOx enable                                            |

|      |      |           | 0: SERVOx disable                                           |

|      |      |           | SERVOx Continuous Mode                                      |

| 30   | СМ   | R/W       | 1: SERVOx Continuous Mode enable                            |

|      |      |           | 0: SERVOx Continuous Mode disable                           |

|      |      |           | Inverse SERVO signal                                        |

| 29   | INVS | R/W       | 0: default SERVO out '0', SPH specify 'I', SPL specify "0". |

|      |      |           | 1: Inverse output signal of upper case                      |

| 28   | Rsvd | RO        | Reserved                                                    |

| 27-0 | RC   | R/W       | SERVOx Repeat Count. It is used when CM=0.                  |

#### Technical Reference

## Vortex86DX South Bridge Configuration Registers

| Registe | er Offse | t:         | 01h – 0 | 0h     |       |   |   |    |   |   |   |   |   |   |   |

|---------|----------|------------|---------|--------|-------|---|---|----|---|---|---|---|---|---|---|

| Registe | er Name  | <b>)</b> : | Vendor  | ID Reg | ister |   |   |    |   |   |   |   |   |   |   |

| Reset V | alue:    |            | 17F3h   |        |       |   |   |    |   |   |   |   |   |   |   |

| 15      | 14       | 13         | 12      | 11     | 10    | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|         |          |            |         |        |       |   | V | ID |   |   |   |   |   |   |   |

| Bit  | Name | Attribute | Description                                                               |

|------|------|-----------|---------------------------------------------------------------------------|

| 15-0 | VID  | RO        | This register contains a 16-bit value assigned to South Bridge Vendor ID. |

| Registe | r Offse | et: | 03h – 0            | 2h |    |   |   |    |   |   |   |   |   |   |   |

|---------|---------|-----|--------------------|----|----|---|---|----|---|---|---|---|---|---|---|

| Registe | r Name  | e:  | Device ID Register |    |    |   |   |    |   |   |   |   |   |   |   |

| Reset V | alue:   |     | 6031h              |    |    |   |   |    |   |   |   |   |   |   |   |

| 15      | 14      | 13  | 12                 | 11 | 10 | 9 | 8 | 7  | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|         |         |     |                    |    |    |   | D | ID |   |   |   |   |   |   |   |

| Bit  | Name | Attribute | Description                                                           |

|------|------|-----------|-----------------------------------------------------------------------|

| 15-0 | DID  | RO        | This register contains a 16-bit value to specify a particular device. |

| R            | eg | iste | er O | ffse | et: |    | 4Bh  | - 4                                           | 8h   |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |          |   |   |

|--------------|----|------|------|------|-----|----|------|-----------------------------------------------|------|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|----------|---|---|

| R            | eg | iste | er N | amo  | e:  | I  | Buff | Buffer Strength/Clock Output Control Register |      |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |          |   |   |

| Reset Value: |    |      |      |      |     |    | 3FF  | F36                                           | 600h | ۱  |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   |          |   |   |

|              | 31 | 30   | 29   | 28   | 27  | 26 | 25   | 24                                            | 23   | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2        | 1 | 0 |

|              |    |      |      |      |     |    |      |                                               |      |    |    |    |    |    |    |    |    |    |    |    |    |    |   |   |   |   |   |   |   | <u> </u> |   |   |

| Rvd | GPIO4_DRV | GPIO3_3_DRV | GPIO3_2_DRV | GPIO3_1_DRV | GPIO2_DRV | GPIO1_DRV | GPIO0_DRV | Rvd | PCI_CTL_SR | PCI_CTL_DRV | PCI_DT_SR | PCI_DT_DRV | Rvd | ISACK_CTL | 14M_CTL |  | 25M_CTL |  |

|-----|-----------|-------------|-------------|-------------|-----------|-----------|-----------|-----|------------|-------------|-----------|------------|-----|-----------|---------|--|---------|--|

|-----|-----------|-------------|-------------|-------------|-----------|-----------|-----------|-----|------------|-------------|-----------|------------|-----|-----------|---------|--|---------|--|

| Bit   | Name      | Attribute | Description                                               |

|-------|-----------|-----------|-----------------------------------------------------------|

| 31-30 | Rvd       | RO        | Reserved                                                  |

|       |           |           | GPIO4[7-0]/SERVO[31-24]/COM1 Driving Current Control      |

|       |           |           | 00: 4mA                                                   |

| 29-28 | GPIO4_DRV | RW        | 01: 8mA                                                   |

|       |           |           | 10: 12mA                                                  |

|       |           |           | 11: 16mA (default)                                        |

| 21-20 | GPIO2_DRV | RW        | GPIO2[7-0]/SERVO[23-16]/SA[31-24] Driving Current Control |

| Bit   | Name      | Attribute | Description                                    |

|-------|-----------|-----------|------------------------------------------------|

|       |           |           | 00: 4mA                                        |

|       |           |           | 01: 8mA                                        |

|       |           |           | 10: 12mA                                       |

|       |           |           | 11: 16mA (default)                             |

|       |           |           | GPIO1[7-0]/SERVO[15-8] Driving Current Control |

|       |           |           | 00: 4mA                                        |

| 19-18 | GPIO1_DRV | RW        | 01: 8mA                                        |

|       |           |           | 10: 12mA                                       |

|       |           |           | 11: 16mA (default)                             |

|       |           |           | GPIO0[7-0]/SERVO[7-0] Driving Current Control  |

|       |           |           | 00: 4mA                                        |

| 17-16 | GPIO0_DRV | RW        | 01: 8mA                                        |

|       |           |           | 10: 12mA                                       |

|       |           |           | 11: 16mA (default)                             |

| Register Offset: | BFh – BCh                       |

|------------------|---------------------------------|

| Register Name:   | On-Chip Device Control Register |

| Reset Value:     | 0000000h                        |

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

| Reserved UDP G1P G1P |  |  | IDEP |

|----------------------|--|--|------|

|----------------------|--|--|------|

| Bit | Name | Attribute | Description                         |

|-----|------|-----------|-------------------------------------|

|     |      |           | ON-Chip SERVO power-down control    |

| 20  | SVP  | R/W       | 0: on-chip SERVO activate (default) |

|     |      |           | 1: on-chip SERVO power-down         |

Register Offset:C3-C0hRegister Name:Internal Peripheral Feature Control RegisterReset Value:032C0500h

| 31 30 | 29 28 27 | 26 25 24 | 23 22 21 | 20 19 18 | 17     | 16     | 15   | 14    | 13   | 12   | 11   | 10   | 9    | 8    | 7     | 6    | 5     | 4     | 3   | 2     | 1     | 0     |

|-------|----------|----------|----------|----------|--------|--------|------|-------|------|------|------|------|------|------|-------|------|-------|-------|-----|-------|-------|-------|

| Rsvd  | IO16W    | IO8W     | MEM16W   | MEM8W    | ISACLK | Int_zw | Rsvd | IDEIS | PWM2 | PWM1 | PWM0 | FCDC | MCLK | EMIQ | PINS6 | SFCE | PINS5 | PINS4 | CPS | PINS2 | PINS1 | PINSO |

**Technical Reference**

| Bit | Name  | Attribute | Description                                          |

|-----|-------|-----------|------------------------------------------------------|

|     |       |           | PINS selection for COM1 and GPIO Port 4              |

| 1   | PINS1 | R/W       | 0: 8 PINs for COM1(default)                          |

|     |       |           | 1: 8 PINs for GPIO port 4                            |

|     |       |           | PINS selection for External SPI and GPIO Port3 [3-0] |

| 0   | PINS0 | R/W       | 0: 4 pins for GPIO port3 [3-0] (default)             |

|     |       |           | 1: 4 pins for external SPI                           |

# Register Offset:CBh – C8hRegister Name:Internal Peripheral Feature Control Register IIReset Value:0000000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

| GS[31-24] GS[23-16] GS[15-8] GS[7-0] |  |

|--------------------------------------|--|

|--------------------------------------|--|

| Bit     | Name      | Attribute | Description                                                                 |                                          |

|---------|-----------|-----------|-----------------------------------------------------------------------------|------------------------------------------|

|         |           |           | GPIO_P4[7-0] and SERVO[31-24] selection. This register is used only when SB |                                          |

| 31-24   | GS[31-24] | R/W       | register C0h bit1 is "1".                                                   |                                          |

| 51-24   | 63[31-24] |           | 0: PINS for GPIO_P4 (default)                                               |                                          |

|         |           |           | 1: PINS for SERVO                                                           |                                          |

|         |           |           | GPIO_P2[7-0] and SERVO[23-16] selection. This register is used only when    |                                          |

| 23 – 16 | GS[23-16] | R/W       |                                                                             | STRAP[1] (NB register 60h bit19) is "1". |

| 23 - 10 | 63[23-10] |           | 0: PINS for GPIO_P2 (default)                                               |                                          |

|         |           |           | 1: PINS for SERVO                                                           |                                          |

|         |           |           | GPIO_P1[7-0] and SERVO[15-8] selection.                                     |                                          |

| 15 – 8  | GS[15-8]  | R/W       | 0: PINS for GPIO_P1 (default)                                               |                                          |

|         |           |           | 1: PINS for SERVO                                                           |                                          |

|         |           |           | GPIO_P0[7-0] and SERVO[7-0] selection.                                      |                                          |

| 7 – 0   | GS[7-0]   | R/W       | 0: PINS for GPIO_P0 (default)                                               |                                          |

|         |           |           | 1: PINS for SERVO                                                           |                                          |

Register Offset:D3h – D0hRegister Name:Internal SERVO Control RegisterReset Value:0000000h

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

| Reserved C 등 Rsvd SIRT | UIOA Reserved |

|------------------------|---------------|

|------------------------|---------------|

Technical Reference

| Bit   | Name | Attribute | Description                                                                       |

|-------|------|-----------|-----------------------------------------------------------------------------------|

| 31-25 | Rsvd | RO        | Reserved                                                                          |

|       |      |           | Servo Clock selection                                                             |

| 24    | CLKS | R/W       | 0: 10MHz (default)                                                                |

|       |      |           | 1: 50MHz                                                                          |

|       |      |           | Enable/Disable Internal SERVO IO Address Decode                                   |

| 23    | UE   | R/W       | 0: Disable (Default)                                                              |

|       |      |           | 1: Enable                                                                         |

| 22-20 | Rsvd | RO        | Reserved                                                                          |

|       |      |           | SERVO IRQ Routing Table                                                           |

|       |      |           | Bit19 Bit18 Bit17 Bit16 Routing Table                                             |

|       |      |           | 0 0 0 Disable.                                                                    |

|       |      |           | 0 0 0 1 IRQ[9]                                                                    |

|       |      |           | 0 0 1 0 IRQ[3]                                                                    |

|       |      |           | 0 0 1 1 IRQ[10]                                                                   |

|       |      |           | 0 1 0 0 IRQ[4]                                                                    |

|       |      |           | 0 1 0 1 IRQ[5]                                                                    |

|       |      |           | 0 1 1 0 IRQ[7]                                                                    |

| 19-16 | SIRT | R/W       | 0 1 1 1 IRQ[6]                                                                    |

|       |      |           | 1 0 0 0 IRQ[1]                                                                    |

|       |      |           | 1 0 0 1 IRQ[11]                                                                   |

|       |      |           | 1 0 1 0 Reserved                                                                  |

|       |      |           | 1 0 1 1 IRQ[12]                                                                   |

|       |      |           | 1 1 0 0 Reserved                                                                  |

|       |      |           | 1 1 0 1 IRQ[14]                                                                   |

|       |      |           | 1 1 1 0 Reserved                                                                  |

|       |      |           | 1 1 1 1 IRQ[15]                                                                   |

|       |      |           | These four bits are used to route SERVO IRQ to any 8259 Interrupt lines. The BIOS |

|       |      |           | should be used to inhibit the setting of the reserved value.                      |

| 15-9  | UIOA | R/W       | Internal SERVO IO Address. The Bit[15:9] contain the base IO address A[15:9] of   |

|       |      |           | internal SERVO.                                                                   |

| 8-0   | Rsvd | RO        | Reserved. All are '0's. Writing any value to these bits causes no effect.         |

# **4.SPI Registers**

(Base Address Refers to the Register of index 43h-40h, IDSEL = AD11/NB of PCI Configuration Register)

| IO Address | Register Name                           |  |  |  |  |  |

|------------|-----------------------------------------|--|--|--|--|--|

| BA + 00h   | Flash SPI Output Data Register          |  |  |  |  |  |

| BA + 01h   | Flash SPI Input Data Register           |  |  |  |  |  |

| BA + 02h   | Flash SPI Control Register              |  |  |  |  |  |

| BA + 03h   | Flash SPI Status Register               |  |  |  |  |  |

| BA + 04h   | BA + 04h Flash SPI Chip-Select Register |  |  |  |  |  |

| BA + 05h   | Flash SPI Error Status Register         |  |  |  |  |  |

| BA + 08h   | External SPI Output Data Register       |  |  |  |  |  |

| BA + 09h   | External SPI Input Register             |  |  |  |  |  |

| BA + 0Ah   | External SPI Control Register           |  |  |  |  |  |

| BA + 0Bh   | External SPI Status Register            |  |  |  |  |  |

| BA + 0Ch   | External SPI Chip Select Register       |  |  |  |  |  |

| BA + 0Dh   | External SPI Error Status Register      |  |  |  |  |  |

#### BASE\_ADDR defined on NB PCI CFG 40h

| Registe        | r Offse | et: | BASE_ADDR+00h                  |   |   |   |   |

|----------------|---------|-----|--------------------------------|---|---|---|---|

| Register Name: |         |     | Flash SPI Output Data Register |   |   |   |   |

| Reset Value:   |         |     |                                |   |   |   |   |

| 7              | 6       | 5   | 4                              | 3 | 2 | 1 | 0 |

OUTDAT

| Bit | Name       | Attribute | Description                                           |

|-----|------------|-----------|-------------------------------------------------------|

| 7-0 | OUTDA<br>T | WO        | Data output to SPI when write. No function when read. |

| Register Offset: |       |   | BASE_                    | ADDR+ | -01h |   |   |  |  |

|------------------|-------|---|--------------------------|-------|------|---|---|--|--|

| Register Name:   |       |   | Flash SPI Input Register |       |      |   |   |  |  |

| Reset Value:     |       |   | FFh                      |       |      |   |   |  |  |

| 7                | 6     | 5 | 4                        | 3     | 2    | 1 | 0 |  |  |

|                  | INDAT |   |                          |       |      |   |   |  |  |